Dina taun 1965, ko-pangadeg Intel Gordon Moore ngajelaskeun naon anu janten "Hukum Moore." Salila leuwih ti satengah abad, éta ngadukung paningkatan anu ajeg dina kinerja sirkuit terpadu (IC) sareng turunna biaya — dasar téknologi digital modéren. Singkatna: jumlah transistor dina chip sakitar dua kali lipat unggal dua taun.

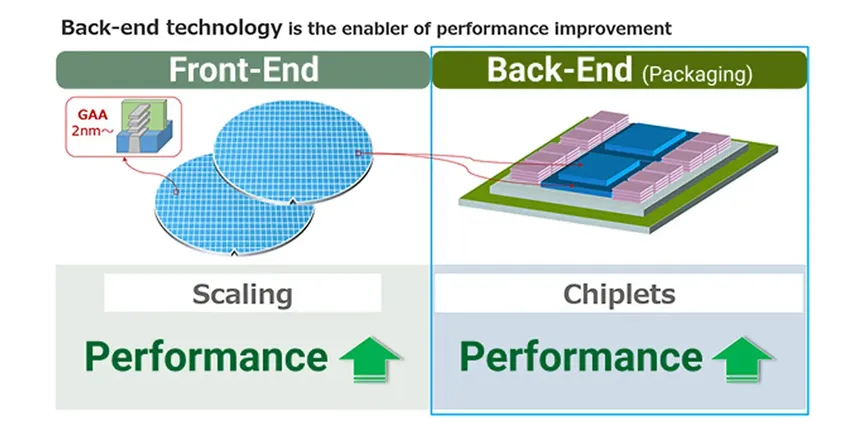

Mangtaun-taun, kamajuan ngalacak irama éta. Ayeuna gambaranana robih. Susut salajengna parantos janten sesah; ukuran fitur turun ka ngan ukur sababaraha nanometer. Insinyur ngalaman wates fisik, léngkah prosés anu langkung rumit, sareng biaya anu ningkat. Géométri anu langkung alit ogé ngirangan hasil, ngajantenkeun produksi volume anu luhur langkung sesah. Ngawangun sareng ngoperasikeun pabrik anu canggih meryogikeun modal sareng kaahlian anu ageung. Ku kituna, seueur anu ngabantah Hukum Moore kaleungitan kakuatan.

Parobahan éta parantos muka panto kana pendekatan énggal: chiplets.

Chiplet nyaéta die leutik anu ngalaksanakeun fungsi anu khusus—intina mah sapotong tina naon anu baheulana hiji chip monolitik. Ku cara ngahijikeun sababaraha chiplet dina hiji pakét, pabrik tiasa ngarakit sistem anu lengkep.

Dina jaman monolitik, sadaya fungsi hirup dina hiji dadu ageung, janten cacad di mana waé tiasa ngarusak sadayana chip. Kalayan chiplet, sistem diwangun tina "dadu anu dikenal-saé" (KGD), anu sacara dramatis ningkatkeun hasil sareng efisiensi manufaktur.

Integrasi hétérogén—ngagabungkeun dies anu diwangun dina node prosés anu béda sareng pikeun fungsi anu béda—ngajadikeun chiplets hususna kuat. Blok komputasi kinerja tinggi tiasa nganggo node panganyarna, sedengkeun sirkuit mémori sareng analog tetep dina téknologi anu dewasa sareng hemat biaya. Hasilna: kinerja anu langkung luhur kalayan biaya anu langkung handap.

Industri otomotif hususna kataji. Pabrikan mobil utama nganggo téknik ieu pikeun ngembangkeun SoC dina kendaraan ka hareup, kalayan target diadopsi massal saatos taun 2030. Chiplet ngamungkinkeun aranjeunna pikeun skala AI sareng grafis langkung efisien bari ningkatkeun hasil—ningkatkeun kinerja sareng fungsionalitas dina semikonduktor otomotif.

Sababaraha suku cadang otomotif kedah nyumponan standar kaamanan fungsional anu ketat sahingga ngandelkeun node anu langkung lami sareng kabuktosan. Samentawis éta, sistem modéren sapertos bantosan supir canggih (ADAS) sareng kendaraan anu ditetepkeun ku parangkat lunak (SDV) meryogikeun langkung seueur komputasi. Chiplet ngahubungkeun jurang éta: ku ngagabungkeun mikrokontroler kelas kaamanan, mémori anu ageung, sareng akselerator AI anu kuat, produsén tiasa nyaluyukeun SoC kana kabutuhan unggal produsén mobil—langkung gancang.

Kaunggulan ieu ngaleuwihan otomotif. Arsitéktur chiplet nyebar ka AI, telekomunikasi, sareng domain sanésna, ngagancangkeun inovasi di sakumna industri sareng gancang janten pilar roadmap semikonduktor.

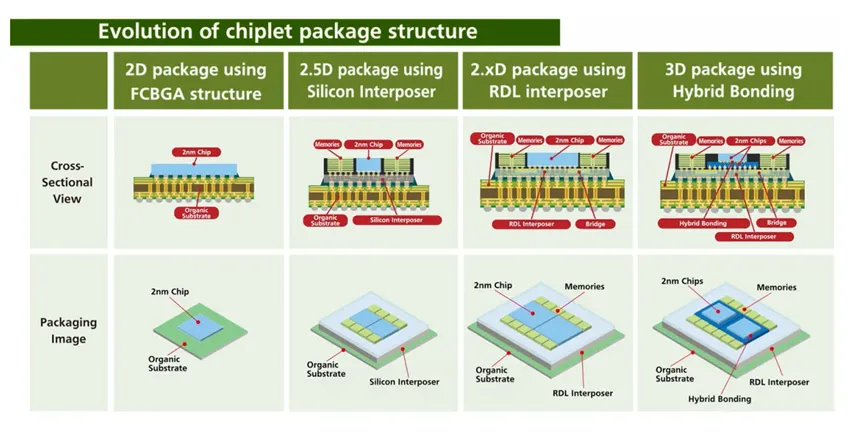

Integrasi chiplet gumantung kana sambungan die-to-die anu kompak sareng kecepatan tinggi. Anu jadi pendorong konci nyaéta interposer—lapisan panengah, seringna silikon, di handapeun die anu ngarutekeun sinyal sapertos papan sirkuit alit. Interposer anu langkung saé hartosna gandengan anu langkung pageuh sareng pertukaran sinyal anu langkung gancang.

Bungkusan canggih ogé ningkatkeun pangiriman daya. Susunan sambungan logam leutik anu padet antara dies nyayogikeun jalur anu lega pikeun arus sareng data bahkan dina rohangan anu sempit, ngamungkinkeun transfer bandwidth anu luhur bari ngamangpaatkeun daérah pakét anu terbatas sacara efisien.

Pamarekan umum ayeuna nyaéta integrasi 2.5D: nempatkeun sababaraha die gigireun dina interposer. Léngkah salajengna nyaéta integrasi 3D, anu numpuk die sacara vertikal nganggo vias silikon-liwat (TSV) pikeun kapadetan anu langkung luhur.

Ngahijikeun desain chip modular (misahkeun fungsi sareng jinis sirkuit) sareng susunan 3D ngahasilkeun semikonduktor anu langkung gancang, langkung alit, sareng langkung hemat énergi. Ngahijikeun mémori sareng komputasi nyayogikeun bandwidth anu ageung kana kumpulan data anu ageung—cocog pikeun AI sareng beban kerja kinerja tinggi anu sanés.

Nanging, susunan vertikal mawa tantangan. Panas langkung gampang akumulasi, anu ngahesekeun manajemen sareng hasil termal. Pikeun ngungkulan ieu, para panaliti nuju ngamajukeun metode pengemasan énggal pikeun nanganan kendala termal anu langkung saé. Sanaos kitu, moméntumna kuat: konvergénsi chiplet sareng integrasi 3D sacara lega dianggap salaku paradigma anu ngaganggu — siap pikeun mawa obor dimana Hukum Moore eureun.

Waktos posting: 15-Okt-2025